Hardware & Security

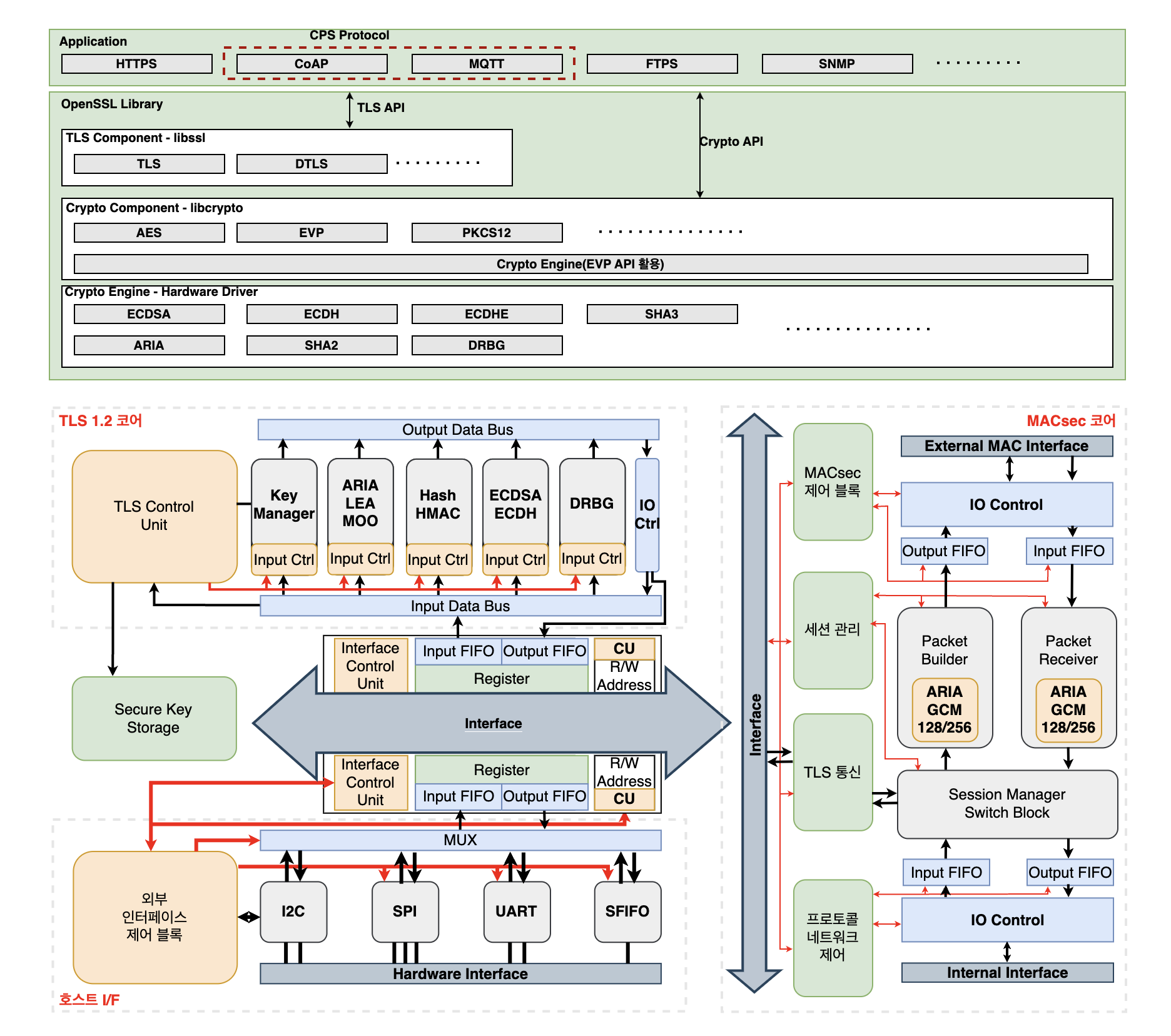

TLS/SSL(TLS1.2, TLS1.3)지원 보안칩 개발 연구(Research on TLS Security Chip Optimization and Implementation)

- –

- TLS 1.2 및 보안 표준 프로토콜 호환 칩 FPGA 구현 및 ASIC(공정) 구현

- –

- 보안 칩과 연동을 위한 TLS/SSL 라이브러리 API(OpenSSL, MbedTLS, WolfSSL, GnuSSL 등) 구현 및 최적화 연구

- –

- CPS(Cyber Physical System) 응용 프로토콜(CoAP, MQTT 등) 호환 암호 코어 및 인터페이스 개발

- –

- 실시간 제어 프로토콜(PROFINET, ModBus 등)의 보안성 제공을 위한 기술 연구

- –

- 양자내성암호(Post Quantum cryptography) 최적화 구현 및 양자내성암호 TLS 라이브러리/CPS 응용 프로토콜 연동 연구

- –

- 블록 암호, 스트림 암호, 타원곡선 암호 등 암호 모듈 고속화/최적화 및 물리채널 공격( DPA, CPA, EM Attack, Timing Attack 등) 방지 기법 연구

- –

- HMAC, DRBG, KDF 등을 활용한 키 생성 프로토콜 및 제어 모듈 구현 및 최적화 연구

- –

- CPS(Cyber Physical System) 응용 프로토콜(CoAP, MQTT 등) 호환 암호 코어 및 인터페이스 개발

- –

- End-To-End 보안 및 유선/무선 네트워크 보안성을 위한 Layer2 보안(MACsec), Layer3 보안(IPSec) 하드웨어 구현 및 고속화 기법 연구

Hardware 기반 딥러닝 가속기 연구(Research on Hardware Based Deep Learning Accelerator)

- –

- Real-Time Object Detection Model(Yolo v2, Yolo v4 등)에 대한 RTL(Register Transfer Level) 기반 딥러닝 추론 가속회로 Verilog 구현 및 FPGA/ASIC 개발

- –

- 딥러닝 가속기 입력 데이터(Image Data, Weight Data)에 대한 데이터 전처리(Fixed Point, Dynamic Fixed Point, Round up 기법, Floating Point 연산기 최적화 등) 및 객체 탐지 결과(Bounding box, Class) 데이터 후처리 기법 연구

- –

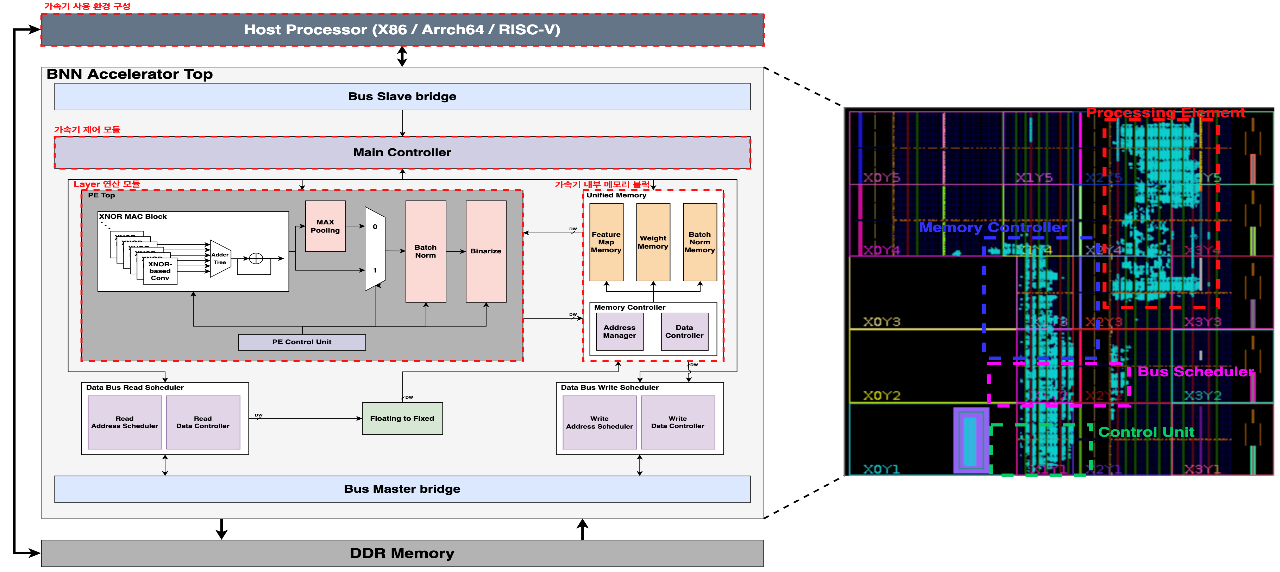

- BNN(Binarized Neural Network) 기반 추론 연산 가속 회로 Verilog 구현 및 호스트 프로세서와의 연동을 통한 System On Chip 개발

- –

- 외부 메모리 저장 파라미터에 대한 DRAM 타겟 공격(Bit Flip Attack, Code Corruption Attack, EM Attack 등) 방어 기법(데이터 무결성 및 기밀성 보장 구조) 연구

[딥러닝 가속기 설계 구조]

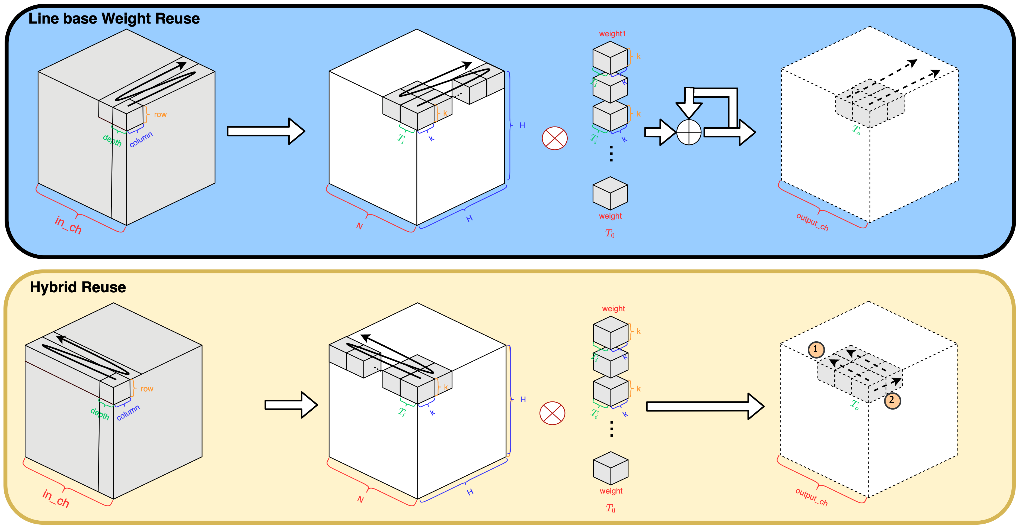

[내부 메모리 스케줄링 기법 최적화 연구]

- –

- 딥러닝 가속기에 대한 물리채널 공격(Power Analysis, Timing Attack, Glitch Attack 등) 방어 기법 연구

- –

- 딥러닝 가속기 메모리 스케줄링 최적화(Line based Reuse, Hybrid Reuse) 기법 연구

- –

- Binarized Layer 연산기 최적화 기법(Logic Gate 기반 Binarized Convolution Method, Bit Shift 기반 Batch Normalization 등) 연구

시스템 구조(RISC-V, ARM, Intel) 및 보안 연구(Research on System Architecture and Security)

- –

- 저사양 및 임베디드 디바이스를 위한 32-bit/64-bit 코프로세서(Coprocessor) 구조 설계 및 개발 연구

- –

- 명령어 파이프라인 최적화 연구(Out-Of-Order Completion) 및 명령어 확장(Vector Processing Unit) 연구

[명령어 파이프라인 최적화 연구]

- –

- ARIA-GCM 및 HMAC 기반 메모리 격리(무결성/기밀성 보장) 기술 연구(키, IV 등 파라미터 보호 기법, 초기화 및 인터페이스 차단 등)

- –

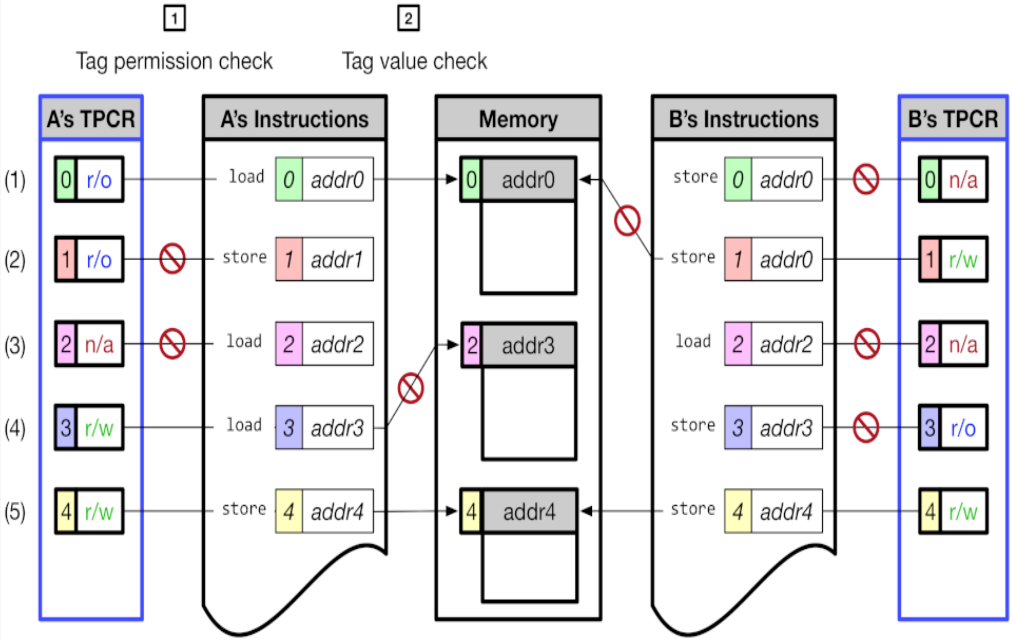

- RISC-V ISA(Instruction Set Architecture) 및 PMP(Physical Memory Protection)를 활용한 명령어 수준의 도메인 격리(Domain Isolation) 및 TMA(Tagged Memory Architecture)기술 연구

[명령어 수준의 도메인 격리 기술 연구]

[Tagged Memory Extension 기술 연구]

+82-51-510-1010

+82-51-510-1010